RaspberryPIの出力を192kHzにリサンプリングしているので、出力されるBCLKは12.288MHzとなっている。そこで、ジッタクリーナーの FRQSEL を HMHM に設定する。

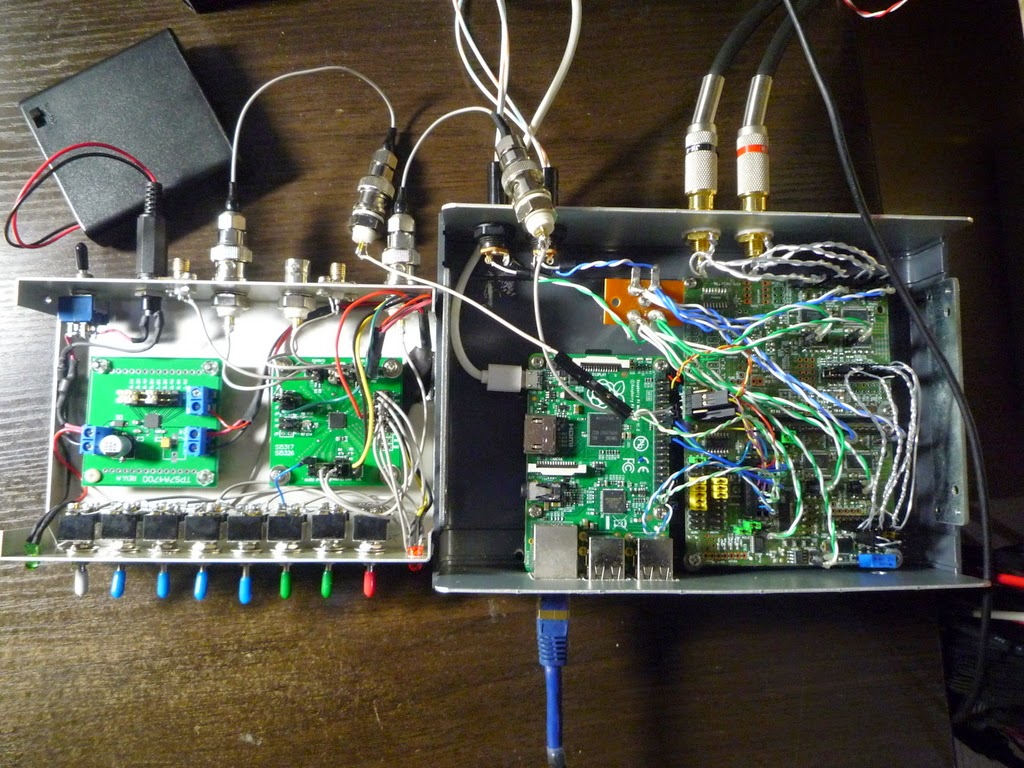

(1/5追記、RaspberryPiのBCLK(BならP5の3PIN、B+ならJ8の12PIN)をジッタークリーナーのCKIN+に、BCLK近くのGNDをジッタクリーナーのCKIN-に入力する。PlanNO.70、FRQTBL=L、FRQSEL=HMHM、BWSEL=HM、に設定。CKOUT1+をタンデム基板のJCCN1の7PINに、CKOUT1-をJCCN1の8PINに入力する。)(できれば、CKIN-にはBCLKを反転させた信号を入れ、CKIN+とCKIN-に差動で入力するとより効果が高いようだ。)

うおー!これりゃあびっくり。音がより静かになり、解像度が増し、力強さが増し、またふくよかさも増している。既に最高の音だったのに、これ以上良くなるなんて思いもよらなかった。もっと早く試してみればよかった。これは凄い。

(参考)

半導体計測屋さんの昨年10月5日のブログで、「VolumioのI2SのBitCLKは、700MHzから生成してるから1.4nsecのジッターが必ず載る」と言われていることを検証しておられる。

http://zx900a.blogspot.jp/2014/10/volumioiisbclk-700mh1.html

「ジッター輝線を見ると、立下りは毎回同じだが、立上りだけが2本に分かれる、そのズレ具合は2nsecくらいで、RMS値にすると1.4nsec位になる、ただし、ずれるのは毎回では無く、248クロック毎に一発ずれる。」とのこと。

このジッターはマスタ基板のSi5317一段だけでは完全に取り切れず、別途、RaspberryPiのBCLKをジッタークリーニングすれば、この248クロック毎の14nsecジッターを取り除くことができるということらしい。

尚、半導体計測屋さんによれば、「ジッタークリーナを2段にする場合は、初段を精細レンジにして、

後段を荒レンジにすると具合がいい」「その理由は、Si5317自身も自己ジッタを持っていて、その発生は荒レンジの方が少ないから、最終的に出てくるクロックのジッタが減る」との事。

asoyaji さま

返信削除明けましておめでとうございます。

Raspberry PiのジッターはAuido出力で比較した結果をみると悪いようです。

https://hifiduino.files.wordpress.com/2014/11/i2sphasenoise-2.png

http://dangerousprototypes.com/forum/viewtopic.php?f=19&t=6089

GUIや使い勝手優先で使うなら便利だと思いますがマイコンDDCはASICに比べるとノイズ面も含めて色々不利な点は多いです。

ジッタークリーナーですがリファレンスXA-XBの精度が入力クロックよりも良くないと好結果は出ません。

ジッタークリーナー2台使う場合はBCLKにカスケードで入れるのか一台目で38MHzをクリーニングして2台目のREFにするのかでしょうね。

年末からSi5328を動かしていますがまだ十分なデータが取れていません。

どちらにしてもジッタークリーナーの本領を発揮するには差動信号での入出力が必要なようです。

ロックレンジが0.1Hz~2HzのSi5328だとリファレンスもかなりシビアです。

その為にOCXOを改造してデータ取ってましたがCDの768fsだとこのまま使っても十分かと思います。

Si5344も発売開始になったのでルビジウムリファレンスのジッタークリーナーもプロジェクト候補です。

旭化成から出た768KHz対応シリーズにサンプルレートコンバーターのAK4317がありますが同等な物を見つけました。

DSD,DoP対応、SPDIFで384KHz32ビット伝送できるようです。

http://www.comtrue-inc.com/

FN1242Aに384KHz24bitを入れても音は出ますね。

以前 可変クロックでES9018SのMCLKを150MHzくらいまで上げても音は出ました。

今ならAK4490EQが面白そうですね。

iinoさん

削除ご無沙汰しています。

昨年は、年初から年末までタンデム基板のみの1年でした。途中、RaspberryPi+I2SというとんでもないミニPCが現われて、まさにとんでもないことが起きた1年でした。

ジッタークリーナーは、いまだに作っていただいたSi5317です。ただ、更に低ジッターなものと言われると心惹かれますが、マイコン制御ものは私には手が出ません。

RaspberryPi(I2S出力)+タンデム基板は、ほんとうに次元の違う音です。この高音質の秘密がわかれば、PCオーディオの世界も更に飛躍できると思うのです。

是非ともお知恵をお貸しください。

今年もよろしくお願いいたします。

早速追試されたようですね。私の正月早々のブレークスルーがRaspberry PiのBCKのジッタークリーニングでした。私の場合TDA1543を使っていますので、2段にする必要がなくナローレンジ一発です。ジッタークリーナーの電源の品質が音質にも相当シビアに効いてきます。

返信削除Raspberry Piですがスレーブでもつかえるような記事をみつけましたので、質のよいADCをつかって外部からのクロックでDATAを生成できたらと思っています。

たくぼんさん

削除BCLKのジッタークリーナー効きますね!

更に高級な音になりました。

最新のジッタークリーナーも試してみたいのですがマイコンは難しくもし使いこなされたら私にも教えてください。今年もよろしくお願いいたします。